CC253x/4x User's Guide (Rev. F)

CC253x System-on-Chip Solution for 2.4-GHz IEEE 802.15.4 ZigBee® Applications

CC2540/41 System-on-Chip Solution for 2.4- GHz Bluetooth® low energy Applications

User's Guide Руководство пользователя

Literature Number: SWRU191F

Скачать оригинал (eng)

Cодержание

Предисловие

CC2540 и CC2541 - это экономичные решения с низким энергопотреблением и истинной системой на кристалле (SoC) для приложений с низким энергопотреблением Bluetooth. Они позволяют создавать надежные главные или подчиненные узлы BLE при очень низких общих затратах на спецификацию. CC2540 и CC2541 сочетают в себе превосходную производительность ведущего радиочастотного приемопередатчика с микроконтроллером 8051 с расширенным отраслевым стандартом, встроенной программируемой флэш-памятью, 8 КБ ОЗУ и многими другими мощными вспомогательными функциями и периферийными устройствами. CC2540 и CC2541 подходят для систем, где требуется очень низкое энергопотребление. Доступны очень маломощные режимы сна. Короткое время перехода между режимами работы также обеспечивает низкое энергопотребление.

CC2540 выпускается в двух разных версиях: CC2540F128 и CC2540F256 с 128 КБ и 256 КБ флэш-памяти соответственно.

CC2541 выпускается в двух разных версиях: CC2541F128 и CC2541F256 с 128 КБ и 256 КБ флэш-памяти соответственно.

CC2541F128 / F256 выпускается в двух разных версиях: CC2541F128 / F256 с 128 и 256 КБ флэш-памяти соответственно.

Решение CC253x System-on-Chip для 2,4 ГГц подходит для широкого спектра применений. Они могут быть легко построены на основе стандартных протоколов IEEE 802.15.4 (сетевой протокол RemoTI ™, программное обеспечение TIMAC и программное обеспечение Z-Stack ™ для решений, совместимых с ZigBee®) или поверх проприетарного сетевого протокола SimpliciTI ™. Использование, однако, не ограничивается только этими протоколами. Например, семейство CC253x также подходит для реализаций 6LoWPAN и Wireless HART.

Подробные технические данные, такие как энергопотребление и характеристики РЧ, см. В технических характеристиках устройства (Приложение C).

Связанная документация (например, лист данных CC2530 и листок данных CC2540 ) может можно найти в приложении С.

Для получения дополнительной информации о программном обеспечении, которое можно использовать с решением Systemon-Chip CC253x, CC2540 или CC2541 (например, программное обеспечение SmartRF ™ для оценки производительности и функциональности радиосвязи), см. Главу 27, в которой также содержится дополнительная информация о сетевом протоколе RemoTI. сетевой протокол SimpliciTI, программное обеспечение TIMAC, программное обеспечение Z-Stack и программное обеспечение стека BLE.

Предупреждение FCC

Это оборудование генерирует, использует и может излучать радиочастотную энергию и не было проверено насоответствие лимитам вычислительных устройств в соответствии с частью J части 15 правил FCC, которые предназначенs для обеспечения разумной защиты от радиочастотных помех. Операция этого оборудование в других средах может создавать помехи для радиосвязи, в этом случае пользователь за свой счет должен будет принять любые меры, которые могут потребоваться для исправления этого вмешательство.

Если вам нужна помощь

Глоссарий

Устройства

Таблица 0-1. Обзор семейства CC253x

| Feature |

CC2530F32, -F64,

-F128/, -F256

|

CC2531F128,

CC2531F256

|

CC2533F32,

-F64, -F96

|

CC2540F128,

-F256

|

CC2541F128,

-F256

|

| FLASH_SIZE |

32 KB, 64 KB,

128 KB, 256 KB

|

128 KB, 256 KB | 32 KB, 64 KB, 96 KB | 128 KB, 256 KB | 128 KB, 256 KB |

| SRAM_SIZE | 8 KB, 8 KB, 8 KB, 8 KB | 8 KB, 8 KB | 4 KB, 4 KB, 6 KB | 8 KB | 8 KB |

| USB | Not included | Included | Not included | Included | Not included |

| ADC | Included | Included | Not included | Included | Included |

| Battery monitor | Not included | Not included | Included | Not included | Not included |

| I2C | Not included | Not included | Included | Not included | Included |

| Operational amplifier | Included | Included | Not included | Included | Not included |

| Analog comparator | Included | Included | Not included | Included | Included |

Регистрация конвенций

В описаниях регистров каждое поле регистра отображается с символом (R/W), указывающим режим доступа к полю регистра. Значения регистра всегда даются в двоичной записи, если только не префикс 0x, что указывает на шестнадцатеричное обозначение

Таблица 0-2. Соглашения о регистрах битов

| SYMBOL | ACCESS MODE |

| R/W | Read and write |

| R | Read-only |

| R0 | Read as 0 |

| R1 | Read as 1 |

| W | Write-only |

| W0 | Write as 0 |

| W1 | Write as 1 |

| H0 | Hardware clear |

| H1 | Hardware set |

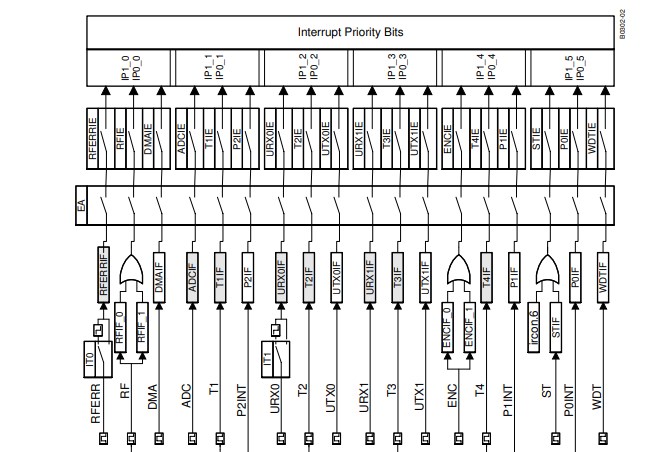

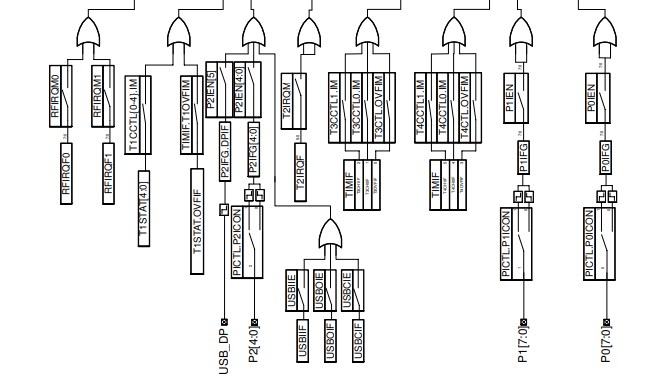

2.5 Прерывания

Определения источников прерываний и векторов прерываний приведены в таблице 2-5.

2.5.1 Маскировка прерывания

Каждое прерывание может быть индивидуально разрешено или запрещено битами разрешения прерывания в SFR разрешения прерывания IEN0, IEN1 и IEN2. SFR, разрешающие прерывания ЦП, описаны ниже и сведены в Таблицу 2-5.

Обратите внимание, что некоторые периферийные устройства имеют несколько событий, которые могут генерировать запрос на прерывание, связанный с этим периферийным устройством. Это относится к Порту 0, Порту 1, Порту 2, Таймеру 1, Таймеру 2, Таймеру 3, Таймеру 4, контроллеру DMA и Радио. Эти периферийные устройства имеют биты маски прерывания для каждого внутреннего источника прерывания в соответствующем регистре SFR или XREG.

- Сбросить флаги прерывания.

- Установите отдельный бит разрешения прерывания в регистре SFR периферийных устройств, если он есть.

- Установите соответствующий отдельный бит разрешения прерывания в регистре IEN0, IEN1 или IEN2 на 1.

- Включите глобальное прерывание, установив бит EA в IEN0 в 1.

- Начните процедуру обслуживания прерывания с соответствующего векторного адреса этого прерывания. Адреса см. в Таблице 2-5.

На рис. 2-4 представлен полный обзор всех источников прерываний и связанных с ними регистров управления и состояния.

Заштрихованные прямоугольники на рис. 2-4 — это флаги прерывания, которые автоматически сбрасываются аппаратным обеспечением при вызове процедуры обслуживания прерывания. _/-\_ указывает на однократный выстрел либо из-за источника уровня, либо из-за фронта формирования. Прерывания без этого должны рассматриваться как инициируемые уровнем (применимо к портам P0, P1 и P2). Поля переключения отображаются в состоянии по умолчанию и _/- ИЛИ -\_указывают на обнаружение нарастающего или спадающего фронта, то есть в какой момент времени генерируется прерывание. Как правило, для импульсных или импульсных источников прерываний следует очищать регистры флагов прерываний ЦП перед очисткой бита флага источника, если он доступен, для флагов, которые не сбрасываются автоматически. Для источников уровня необходимо очистить источник перед очисткой флага процессора.

Обратите внимание, что при очистке флагов исходного прерывания в регистре, содержащем несколько флагов, прерывания могут быть потеряны, если выполняется операция чтения-модификации-записи (даже в одной ассемблерной инструкции), так как она также очищает флаги прерывания, которые стали активными между чтением и операция записи. Флаги прерывания источника (за исключением флагов прерывания контроллера USB) имеют режим доступа R/W0. Это означает, что запись 1 в бит не имеет никакого эффекта, поэтому 1 должна быть записана во флаг прерывания, который нельзя сбрасывать. Например, чтобы очистить бит TIMER2_OVF_PERF (бит 3) T2IRQF в коде C, нужно сделать:

Таблица 2-5. Обзор прерываний

| Номер | Описание | Имя прерывания | Вектор прерывания | Маска прерывания, ЦП | Флаг прерывания, ЦП |

| 0 | ошибка RF core | RFERR | 0x03 | IEN0.RFERRIE | TCON.RFERRIF(1) |

| 1 | ADC end of conversion | ADC | 0x0B | IEN0.ADCIE | TCON.ADCIF(1) |

| 2 | USART 0 RX завершен | URX0 | 0x13 | IEN0.URX0IE | TCON.URX0IF(1) |

| 3 | USART 1 RX завершен | URX1 | 0x1B | IEN0.URX1IE | TCON.URX1IF(1) |

| 4 | Шифрование или дешифрование AES завершено | ENC | 0x23 | IEN0.ENCIE | S0CON.ENCIF |

| 5 | Таймер сна сравнить | ST | 0x2B | IEN0.STIE | IRCON.STIF |

| 6 |

Входы Port-2, USB или I2С

|

P2INT | 0x33 | IEN2.P2IE | IRCON2.P2IF(2) |

| 7 | USART 0 TX завершен | UTX0 | 0x3B | IEN2.UTX0IE | IRCON2.UTX0IF |

| 8 | Передача DMA завершена | DMA | 0x43 | IEN1.DMAIE | IRCON.DMAIF |

| 9 | Таймер 1 (16 бит) захват, сравнение, переполнение | T1 | 0x4B | IEN1.T1IE | IRCON.T1IF(1) (2) |

| 10 | Timer 2 | T2 | 0x53 | IEN1.T2IE | IRCON.T2IF(1) (2) |

| 11 | Таймер 3 (8 бит) захват, сравнение, переполнение | T3 | 0x5B | IEN1.T3IE | IRCON.T3IF(1) (2) |

| 12 | Таймер 4 (8 бит) захват, сравнение, переполнение | T4 | 0x63 | IEN1.T4IE | IRCON.T4IF(1) (2) |

| 13 | Port 0 входы | P0INT | 0x6B | IEN1.P0IE | IRCON.P0IF(2) |

| 14 | USART 1 TX завершен | UTX1 | 0x73 | IEN2.UTX1IE | IRCON2.UTX1IF |

| 15 | Port 1 входы | P1INT | 0x7B | IEN2.P1IE | IRCON2.P1IF(2) |

| 16 | RF общие прерывания | RF | 0x83 | IEN2.RFIE | S1CON.RFIF(2) |

| 17 | Переполнение сторожевого таймера в режиме таймера | WDT | 0x8B | IEN2.WDTIE | IRCON2.WDTIF |

Рисунок 2-4. Обзор прерываний

IEN0 (0xA8) – Interrupt Enable 0 – разрешение прерывания 0

| Bit | Name | Reset | R/W | Описание |

| 7 | EA | 0 | R/W |

Отключает все прерывания.

0: прерывание не подтверждается.

1: каждый источник прерывания отдельно включается или выключается установкой соответствующего бита разрешения.

|

| 6 | - | 0 | R0 | Зарезервирован. Читать как 0 |

| 5 | STIE | 0 | R/W |

Разрешить прерывание таймера сна

0: Прерывание отключено

1: прерывание разрешено

|

| 4 | ENCIE | 0 | R/W |

Включение прерывания шифрования и дешифрования AES

0: Прерывание отключено

1: прерывание разрешено

|

| 3 | URX1IE | 0 | R/W |

USART 1 Разрешение прерывания RX

0: Прерывание отключено

1: прерывание разрешено

|

| 2 | URX0IE | 0 | R/W |

Разрешение прерывания USART0 RX

0: Прерывание отключено

1: прерывание разрешено

|

| 1 | ADCIE | 0 | R/W |

Разрешение прерывания АЦП

0: Прерывание отключено

1: прерывание разрешено

|

| 0 | RFERRIE | 0 | R/W |

Включение прерывания по ошибке RF

0: Прерывание отключено

1: прерывание разрешено

|

IEN1 (0xB8) – Interrupt Enable 1 – разрешение прерывания 1

| Bit | Name | Reset | R/W | Описание |

| 7:6 | - | 00 | R0 | Зарезервирован. Читать как 0 |

| 5 | P0IE | 0 | R/W |

Разрешение прерывания порта 0

0: Прерывание отключено

1: прерывание разрешено

|

| 4 | T4IE | 0 | R/W |

Разрешение прерывания от таймера 4

0: Прерывание отключено

1: прерывание разрешено

|

| 3 | T3IE | 0 | R/W |

Разрешение прерывания от таймера 3

0: Прерывание отключено

1: прерывание разрешено

|

| 2 | T2IE | 0 | R/W |

Разрешение прерывания от таймера 2

0: Прерывание отключено

1: прерывание разрешено

|

| 1 | T1IE | 0 | R/W |

Разрешение прерывания от таймера 1

0: Прерывание отключено

1: прерывание разрешено

|

| 0 | DMAIE | 0 | R/W |

Разрешение прерывания передачи DMA

0: Прерывание отключено

1: прерывание разрешено

|

IEN2 (0x9A) – Interrupt Enable 2 – разрешение прерывания 2

| Bit | Name | Reset | R/W | Описание |

| 7:6 | - | 00 | R0 | Зарезервирован. Читать как 0 |

| 5 | WDTIE | 0 | R/W |

Разрешение прерывания сторожевого таймера

0: Прерывание отключено

1: прерывание разрешено

|

| 4 | P1IE | 0 | R/W |

Разрешение прерывания порта 1

0: Прерывание отключено

1: прерывание разрешено

|

| 3 | UTX1IE | 0 | R/W |

USART 1 Разрешение прерывания TX

0: Прерывание отключено

1: прерывание разрешено

|

| 2 | UTX0IE | 0 | R/W |

USART 0 Разрешение прерывания TX

0: Прерывание отключено

1: прерывание разрешено

|

| 1 | P2IE | 0 | R/W |

Разрешение прерывания порта 2

0: Прерывание отключено

1: прерывание разрешено

|

| 0 | RFIE | 0 | R/W |

Разрешение общего прерывания RF

0: Прерывание отключено

1: прерывание разрешено

|

2.5.2 Обработка прерываний

Когда происходит прерывание, ЦП обращается к адресу вектора прерывания, как показано в таблице 2-5. После запуска службы прерывания ее можно прервать только прерыванием с более высоким приоритетом. Служба прерывания завершается RETI (командой возврата из прерывания). При выполнении RETI ЦП возвращается к инструкции, которая должна была быть следующей в момент возникновения прерывания.

Когда возникает условие прерывания, ЦП также указывает на это, устанавливая бит флага прерывания в регистрах флага прерывания. Этот бит устанавливается независимо от того, разрешено или запрещено прерывание. Если прерывание разрешено, когда установлен флаг прерывания, затем в следующем командном цикле прерывание подтверждается аппаратным обеспечением, вызывая LCALL по соответствующему адресу вектора.

Для ответа на прерывание требуется разное количество времени в зависимости от состояния ЦП в момент возникновения прерывания. Если ЦП выполняет обслуживание прерывания с таким же или более высоким приоритетом, новое прерывание находится в ожидании до тех пор, пока оно не станет прерыванием с наивысшим приоритетом. В других случаях время отклика зависит от текущей инструкции. Самый быстрый ответ на прерывание — семь машинных циклов.

Сюда входит один машинный цикл для обнаружения прерывания и шесть циклов для выполнения LCALL.

ПРИМЕЧАНИЕ. Если прерывание отключено и флаг прерывания опрашивается, ассемблерная инструкция 8051 JBC не должна использоваться для опроса флага прерывания и очистки его при установке. Если инструкция JBC используется, флаг прерывания может быть повторно установлен немедленно.

ПРИМЕЧАНИЕ. Если ассемблерная инструкция XCH A, IEN0 используется для сброса глобального флага разрешения прерывания EA, ЦП может войти в программу прерывания в цикле, следующем за этой инструкцией. В этом случае процедура прерывания выполняется с EA, установленным на 0, что может задержать обслуживание прерываний с более высоким приоритетом.

TCON (0x88) – Interrupt Flags — флаги прерывания

| Bit | Name | Reset | R/W | Описание |

| 7 | URX1IF | 0 | R/W H0 |

Флаг прерывания USART 1 RX. Устанавливается в 1, когда происходит прерывание USART 1 RX, и сбрасывается, когда ЦП обращается к подпрограмме обслуживания прерывания.

0: прерывание не ожидается

1: Ожидание прерывания

|

| 6 | - | 0 | R/W | Зарезервирован. |

| 5 | ADCIF | 0 | R/W H0 |

Флаг прерывания АЦП. Устанавливается в 1, когда происходит прерывание от АЦП, и сбрасывается, когда ЦП обращается к подпрограмме обработки прерывания.

0: прерывание не ожидается

1: Ожидание прерывания

|

| 4 | - | 0 | R/W | Зарезервирован. |

| 3 | URX0IF | 0 | R/W H0 |

USART 0 Флаг прерывания RX. Устанавливается в 1, когда происходит прерывание USART 0, и сбрасывается, когда ЦП обращается к подпрограмме обслуживания прерывания.

0: прерывание не ожидается

1: Ожидание прерывания

|

| 2 | IT1 | 1 | R/W | Зарезервирован. Всегда должен быть установлен в 1. Установка нуля разрешает обнаружение низкоуровневого прерывания, что почти всегда имеет место (однократное, когда инициируется запрос на прерывание). |

| 1 | RFERRIF | 0 | R/W H0 |

Флаг прерывания ошибки радиочастотного ядра. Устанавливается в 1, когда происходит прерывание RFERR, и сбрасывается, когда ЦП обращается к подпрограмме обслуживания прерывания.

0: прерывание не ожидается

1: Ожидание прерывания

|

| 0 | IT0 | 1 | R/W | Зарезервирован. Всегда должен быть установлен в 1. Установка нуля разрешает обнаружение низкоуровневого прерывания, что почти всегда имеет место (однократное, когда инициируется запрос на прерывание). |

S0CON (0x98) – Interrupt Flags 2 - флаги прерывания 2

| Bit | Name | Reset | R/W | Описание |

| 7:2 | - | 0000 00 | R/W | Зарезервирован |

| 1 | ENCIF_1 | 0 | R/W |

прерывание AES. ENC имеет два флага прерывания, ENCIF_1 и ENCIF_0. Установка одного из этих флагов требует прерывания обслуживания. Оба флага устанавливаются, когда сопроцессор AES запрашивает прерывание.

0: прерывание не ожидается

1: Ожидание прерывания

|

| 0 | ENCIF_0 | 0 | R/W |

прерывание AES. ENC имеет два флага прерывания, ENCIF_1 и ENCIF_0. Установка одного из этих флагов требует прерывания обслуживания. Оба флага устанавливаются, когда сопроцессор AES запрашивает прерывание.

0: прерывание не ожидается

1: Ожидание прерывания

|

S1CON (0x9B) – Interrupt Flags 3 - флаги прерывания 3

| Bit | Name | Reset | R/W | Описание |

| 7:2 | - | 0000 00 | R/W | Зарезервирован |

| 1 | RFIF_1 | 0 | R/W |

Общее прерывание RF. RF имеет два флага прерывания, RFIF_1 и RFIF_0. Установка одного из этих флагов требует прерывания обслуживания. Оба флага устанавливаются, когда радио запрашивает прерывание.

0: прерывание не ожидается

1: Ожидание прерывания

|

| 0 | RFIF_0 | 0 | R/W |

Общее прерывание RF. RF имеет два флага прерывания, RFIF_1 и RFIF_0. Установка одного из этих флагов требует прерывания обслуживания. Оба флага устанавливаются, когда радио запрашивает прерывание.

0: прерывание не ожидается

1: Ожидание прерывания

|

IRCON (0xC0) – Interrupt Flags 4 – флаги прерывания 4

| Bit | Name | Reset | R/W | Описание |

| 7 | STIF | 0 | R/W |

Флаг прерывания таймера сна

0: прерывание не ожидается

1: Ожидание прерывания

|

| 6 | - | 0 | R/W | Должен быть записан 0. Запись 1 всегда включает источник прерывания. |

| 5 | P0IF | 0 | R/W |

Флаг прерывания порта 0

0: прерывание не ожидается

1: Ожидание прерывания

|

| 4 | T4IF | 0 | R/W H0 |

Флаг прерывания Таймера 4. Устанавливается в 1, когда происходит прерывание от Таймера 4, и сбрасывается, когда ЦП обращается к подпрограмме обслуживания прерывания.

0: прерывание не ожидается

1: Ожидание прерывания

|

| 3 | T3IF | 0 | R/W H0 |

Флаг прерывания Таймера 3. Устанавливается в 1, когда происходит прерывание от Таймера 3, и сбрасывается, когда ЦП обращается к подпрограмме обслуживания прерывания.

0: прерывание не ожидается

1: Ожидание прерывания

|

| 2 | T2IF | 0 | R/W H0 |

Флаг прерывания Таймера 2. Устанавливается в 1, когда происходит прерывание от Таймера 2, и сбрасывается, когда ЦП обращается к подпрограмме обслуживания прерывания.

0: прерывание не ожидается

1: Ожидание прерывания

|

| 1 | T1IF | 0 | R/W H0 |

Флаг прерывания Таймера 1. Устанавливается в 1, когда происходит прерывание от Таймера 1, и сбрасывается, когда ЦП обращается к подпрограмме обслуживания прерывания.

0: прерывание не ожидается

1: Ожидание прерывания

|

| 0 | DMAIF | 0 | R/W |

Флаг прерывания DMA завершения

0: прерывание не ожидается

1: Ожидание прерывания

|

IRCON2 (0xE8) – Interrupt Flags 5 – флаги прерывания 5

| Bit | Name | Reset | R/W | Описание |

| 7:5 | - | 000 | R/W | Зарезервирован |

| 4 | WDTIF | 0 | R/W |

Флаг прерывания сторожевого таймера

0: прерывание не ожидается

1: Ожидание прерывания

|

| 3 | P1IF | 0 | R/W |

Флаг прерывания порта 1

0: прерывание не ожидается

1: Ожидание прерывания

|

| 2 | UTX1IF | 0 | R/W |

Флаг прерывания USART 1 TX

0: прерывание не ожидается

1: Ожидание прерывания

|

| 1 | UTX0IF | 0 | R/W |

Флаг прерывания USART 0 TX

0: прерывание не ожидается

1: Ожидание прерывания

|

| 0 | P2IF | 0 | R/W |

Флаг прерывания порта 2

0: прерывание не ожидается

1: Ожидание прерывания

|

2.5.3 Приоритет прерывания

Прерывания сгруппированы в шесть групп приоритета прерывания, и приоритет для каждой группы устанавливается регистрами IP0 и IP1. Чтобы присвоить прерыванию более высокий приоритет, то есть его группе прерываний, соответствующие биты в IP0 и IP1 должны быть установлены, как показано в таблице 2-6.

Группы приоритетов прерываний с назначенными источниками прерываний показаны в таблице 2-7. Каждой группе назначается один из четырех уровней приоритета. Пока выполняется запрос на обслуживание прерывания, его нельзя прерывать прерыванием более низкого или того же уровня.

В случае, когда одновременно принимаются запросы на прерывание с одинаковым уровнем приоритета, для определения приоритета каждого запроса используется последовательность опроса, показанная в таблице 2-8. Обратите внимание, что последовательность опроса на Рисунке 2-4 представляет собой алгоритм из Таблицы 2-8, а не то, что опрос выполняется среди битов IP, как показано на рисунке.

IP1 (0xB9) – Interrupt Priority 1 – приоритет прерывания 1

| Bit | Name | Reset | R/W | Описание |

| 7:6 | - | 00 | R/W | Зарезервирован |

| 5 | IP1_IPG5 | 0 | R/W | Группа прерываний 5, бит управления приоритетом 1, см. Таблицу 2-7: Группы приоритетов прерываний |

| 4 | IP1_IPG4 | 0 | R/W | Группа прерываний 4, бит управления приоритетом 1, см. Таблицу 2-7: Группы приоритетов прерываний |

| 3 | IP1_IPG3 | 0 | R/W | Группа прерываний 3, бит управления приоритетом 1, см. Таблицу 2-7: Группы приоритетов прерываний |

| 2 | IP1_IPG2 | 0 | R/W | Группа прерываний 2, бит управления приоритетом 1, см. Таблицу 2-7: Группы приоритетов прерываний |

| 1 | IP1_IPG1 | 0 | R/W | Группа прерываний 1, бит управления приоритетом 1, см. Таблицу 2-7: Группы приоритетов прерываний |

| 0 | IP1_IPG0 | 0 | R/W | Группа прерываний 0, бит управления приоритетом 1, см. Таблицу 2-7: Группы приоритетов прерываний |

IP0 (0xA9) – Interrupt Priority 0 – приоритет прерывания 0

| Bit | Name | Reset | R/W | Описание |

| 7:6 | - | 00 | R/W | Зарезервирован |

| 5 | IP0_IPG5 | 0 | R/W | Группа прерываний 5, бит управления приоритетом 1, см. Таблицу 2-7: Группы приоритетов прерываний |

| 4 | IP0_IPG4 | 0 | R/W | Группа прерываний 4, бит управления приоритетом 1, см. Таблицу 2-7: Группы приоритетов прерываний |

| 3 | IP0_IPG3 | 0 | R/W | Группа прерываний 3, бит управления приоритетом 1, см. Таблицу 2-7: Группы приоритетов прерываний |

| 2 | IP0_IPG2 | 0 | R/W | Группа прерываний 2, бит управления приоритетом 1, см. Таблицу 2-7: Группы приоритетов прерываний |

| 1 | IP0_IPG1 | 0 | R/W | Группа прерываний 1, бит управления приоритетом 1, см. Таблицу 2-7: Группы приоритетов прерываний |

| 0 | IP0_IPG0 | 0 | R/W | Группа прерываний 0, бит управления приоритетом 1, см. Таблицу 2-7: Группы приоритетов прерываний |

Таблица 2-6. Настройка уровня приоритета

| IP1_x | IP0_x | Уровень приоритета |

| 0 | 0 | 0 - самый низкий |

| 0 | 1 | 1 |

| 1 | 0 | 2 |

| 1 | 1 | 3 – самый высокий |

Таблица 2-7. Группы приоритета прерывания

| Группа | Прерывания | ||

| IPG0 | RFERR | RF | DMA |

| IPG1 | ADC | T1 | P2INT |

| IPG2 | URX0 | T2 | UTX0 |

| IPG3 | URX1 | T3 | UTX1 |

| IPG4 | ENC | T4 | P1INT |

| IPG5 | ST | P0INT | WDT |

Таблица 2-8. Последовательность опроса прерывания

| Номер прерывания | Имя прерывания |

Последовательность опроса ↓ |

| 0 | RFERR | |

| 16 | RF | |

| 8 | DMA | |

| 1 | ADC | |

| 9 | T1 | |

| 2 | URX0 | |

| 10 | T2 | |

| 3 | URX1 | |

| 11 | T3 | |

| 4 | ENC | |

| 12 | T4 | |

| 5 | ST | |

| 13 | P0INT | |

| 6 | P2INT | |

| 7 | UTX0 | |

| 14 | UTX1 | |

| 15 | P1INT | |

| 17 | WDT |

4 Управление питанием и часы

Тема ................................................. .................................................. страница

4.1 Управление питанием Введение

Пять различных режимов работы (режимы питания) называются активным режимом, режимом ожидания, PM1, PM2 и PM3 (PM1, PM2 и PM3 также называются спящими режимами). Активный режим является нормальным режимом работы, тогда как PM3 имеет самое низкое энергопотребление. Влияние различных режимов мощности на работу системы показано в таблице 4-1 вместе с опциями регулятора напряжения и генератора.

Таблица 4-1. Режимы питания

| Power Mode | Высокочастотный генератор | Низкочастотный генератор | Регулятор напряжения |

| Конфигурация |

A 32-MHz XOSC

B 16-MHz RCOSC

|

C 32-kHz XOSC

D 32-kHz RCOSC

|

|

| Активный или режим ожидания | A or B | C or D | ON |

| PM1 | None | C or D | ON |

| PM2 | None | C or D | OFF |

| PM3 | None | None | OFF |

Активный режим: полностью функциональный режим. Регулятор напряжения на цифровом ядре включен, и либо 16-МГц RC-генератор, либо 32-МГц кварцевый генератор, либо оба работают. Либо 32-кГц RCOSC, либо 32-кГц XOSC работает.

PM1: регулятор напряжения на цифровой части включен. Ни 32-МГц XOSC, ни 16-МГц RCOSC не работают. Работает либо 32-кГц RCOSC, либо 32-кГц XOSC. Система переходит в активный режим при сбросе, внешнем прерывании или по истечении таймера сна.

PM2: регулятор напряжения на цифровом сердечнике выключен. Ни 32-МГц XOSC, ни 16-МГц RCOSC не работают. Работает либо 32-кГц RCOSC, либо 32-кГц XOSC. Система переходит в активное состояние при сбросе, внешнем прерывании или по истечении таймера сна.

PM3: Регулятор напряжения на цифровом ядре выключен. Ни один из генераторов не работает. Система переходит в активный режим при сбросе или внешнем прерывании.

POR активен в PM2 и PM3, но BOD выключен, что обеспечивает ограниченный контроль напряжения. Если напряжение питания снижается до уровня ниже 1,4 В во время PM2 или PM3, при температуре 70 ° C или выше, а затем восстанавливается до хорошего рабочего напряжения до повторного ввода активного режима, регистры и содержимое ОЗУ сохраняются в PM2. или PM3 может стать измененным. Следовательно, следует соблюдать осторожность при проектировании источника питания системы, чтобы этого не происходило. Напряжение можно периодически точно контролировать, входя в активный режим, так как сброс BOD запускается, если напряжение питания ниже приблизительно 1,7 В.

CC2533 и CC2541 имеют функции для автоматического выполнения проверки CRC сохраненных значений регистра конфигурации в PM2 и PM3, чтобы проверить, что состояние устройства не было изменено во время сна.

Биты в SRCRC.CRC_RESULT указывают, были ли какие-либо изменения, и, включив SRCRC.CRC_RESET_EN, устройство немедленно сбрасывает себя со сбросом сторожевого таймера, если SRCRC.CRC_RESULT не равен 00 (= CRC пропущенных сохраненных регистров) после пробуждения из PM2 или PM3. Регистр SRCRC также содержит бит SRCRC.FORCE_RESET, который может использоваться программным обеспечением для немедленного запуска сброса сторожевого таймера для перезагрузки устройства.

4.1.1 Active and Idle Modes - Активный и режим ожидания

Активный режим - это полнофункциональный режим работы, в котором активны процессор, периферийные устройства и радиопередатчик. Цифровой регулятор напряжения включен.

4.1.2 PM1

В PM1 высокочастотные генераторы отключены (32-МГц XOSC и 16-МГц RCOSC). Регулятор напряжения и включенный генератор с частотой 32 кГц включены. Когда PM1 введен, отключение питания последовательность запускается PM1 используется, когда ожидаемое время до события пробуждения является относительно коротким (менее 3 мс), поскольку PM1 использует последовательность быстрого выключения и включения питания.

4.1.3 PM2

PM2 занимает второе место по энергопотреблению. В PM2 активны сброс при включении питания, внешние прерывания, выбранный генератор с частотой 32 кГц и периферийный таймер отключения. Контакты ввода/вывода сохраняют режим ввода/вывода и заданное значение до входа в PM2. Все остальные внутренние цепи отключены. Регулятор напряжения также выключен. Когда вводится PM2, запускается последовательность выключения питания.

PM2 обычно вводится при использовании таймера сна в качестве события пробуждения, а также в сочетании с внешними прерываниями. PM2 обычно следует выбирать по сравнению с PM1, когда ожидаемое время сна превышает 3 мс Использование меньшего времени ожидания не снижает энергопотребление системы по сравнению с использованием PM1.

4.1.4 PM3

Сброс (POR или внешний) и внешние порты ввода/вывода - единственные функции, которые работают в этом режиме.

Выводы ввода/вывода сохраняют режим ввода/вывода и заданное значение до входа в PM3. Условие сброса или включенное событие внешнего прерывания ввода/вывода пробуждает устройство и переводит его в активный режим (внешнее прерывание начинается с того места, где оно вошло в PM3, тогда как сброс возвращается к выполнению в начале программы). Содержимое ОЗУ и регистров частично сохраняется в этом режиме (см. Раздел 4.6). PM3 использует ту же последовательность выключения и включения питания, что и PM2.

PM3 используется для достижения сверхнизкого энергопотребления при ожидании внешнего события. Его следует использовать, когда ожидаемое время ожидания превышает 3 мс.

4.2 Управление питанием

Включенное прерывание от контактов порта или таймера отключения или сброса при включении питания выводит устройство из других режимов питания и переводит его в активный режим.

При вводе PM1, PM2 или PM3 выполняется последовательность выключения питания. Когда устройство выводится из PM1, PM2 или PM3, оно запускается на частоте 16 МГц и автоматически изменяется на 32 МГц, если CLKCONCMD.OSC был 0 при входе в режим питания (настройка PCON.IDLE). Если CLKCONCMD.OSC был равен 1, когда PCON.IDLE был установлен, то при переходе в режим питания он продолжает работать на частоте 16 МГц.

Инструкция, которая устанавливает бит PCON.IDLE, должна быть выровнена определенным образом для правильной работы. Первый байт инструкции по сборке, следующий сразу за этой инструкцией, не должен быть размещен на 4-байтовой границе. Кроме того, кеш не должен быть отключен (см. CM в описании регистра FCTL в Главе 6). Несоблюдение этого требования может привести к увеличению потребления тока. При условии, что это требование выполнено, первая инструкция по сборке после инструкции, которая устанавливает бит PCON.IDLE, выполняется до ISR прерывания, которое вызвало пробуждение системы, но после пробуждения системы. Если эта инструкция является глобальным отключением прерывания, возможно, что за ней последует код для выполнения после активации, но до обслуживания ISR.

Пример того, как это можно сделать в компиляторе IAR, показан ниже. Команда для установки PCON в 1 помещается в функцию, записанную в коде сборки. В C-файле, вызывающем эту функцию, объявление например

extern void EnterSleepModeDisableInterruptsOnWakeup (void);

используется.

Это означает, что ISR прерывания, которое разбудило систему, не выполняется до тех пор, пока бит IEN0.EA не будет снова установлен позже в коде. Если эта функциональность не нужна, инструкцию CLR EA можно заменить на NOP.

4.3. Регистры управления питанием

SRCRC (0x6262) – Sleep Reset CRC (CC2533 and CC2541 only)

| Bit | Name | Reset | R/W | Description |

| 7 | XOSC_AMP_DET_EN | 0 | R/W |

0: отключить

1: Включить амплитудный детектор для 32-МГц XOSC, только CC2533

|

| 6 | - | 0 | R0 | Зарезервированный. Всегда читай 0 |

| 5 | FORCE_RESET | 0 | R/W |

0: никаких действий

1: принудительный сброс сторожевого таймера.

|

| 4 | - | 0 | R | Зарезервированный |

| 3:2 | CRC_RESULT | 00 | R/W |

00: CRC сохраненных регистров пройден

01: Ошибка низкого значения CRC

10: сбой высокого значения CRC

11: оба значения CRC не выполнены

|

| 1 | - | 0 | R | Зарезервированный |

| 0 | CRC_RESET_EN | 0 | R/W |

0: отключить сброс микросхемы из-за CRC.

1: включить сброс микросхемы, если CRC_RESULT! = 00 после пробуждения из PM2 или PM3.

|

PCON (0x87) – Power Mode Control

| Bit | Name | Reset | R/W | Description |

| 7:1 | - | 0000 000 | R/W | Зарезервировано, всегда пишите как 0000 000. |

| 0 | IDLE | 0 | R0/W H0 |

Управление режимом питания. Запись 1 в этот бит вынуждает устройство переходить в режим питания, установленный SLEEPCMD.MODE (обратите внимание, что MODE = 0x00 AND IDLE = 1 останавливает работу ядра процессора). Этот бит всегда читается как 0.

Все активные прерывания очищают этот бит, когда он активен, и устройство снова переходит в активный режим.

|

SLEEPCMD (0xBE) – Sleep-Mode Control Command - команда управления в спящем режиме

| Bit | Name | Reset | R/W | Description |

| 7 | OSC32K_CALDIS | 0 | R/W |

Отключить калибровку генератора RC 32 кГц

Калибровка RC генератора 0: 32 кГц включена.

Калибровка RC генератора 1: 32 кГц отключена.

Эта настройка может быть записана в любое время, но она не вступит в силу, пока микросхема не будет запущена на 16-МГц высокочастотном RC-генераторе.

|

| 6:3 | - | 000 0 | R0 | Зарезервированный. Всегда пишите как 1 |

| 2 | - | 1 | R/W | Зарезервированный |

| 1:0 | MODE[1:0] | 00 | R/W |

Настройка режима питания

00: Active or Idle mode - активный или режим ожидания

01: режим питания 1 (PM1)

10: режим питания 2 (PM2)

11: режим питания 3 (PM3)

|

SLEEPSTA (0x9D) – Sleep-Mode Control Status - Состояние управления в спящем режиме

| Bit | Name | Reset | R/W | Description |

| 7 | OSC32K_CALDIS | 0 | R |

Состояние калибровки генератора RC 32 кГц

SLEEPSTA.OSC32K_CALDIS показывает текущее состояние отключения калибровки RC 32 кГц. Бит не установлен на то же значение, что и SLEEPCMD.OSC32K_CALDIS, прежде чем микросхема будет запущена на 32-кГц RC генераторе.

|

| 6:5 | - | 00 | R | Зарезервированный |

| 4:3 | RST[1:0] | XX | R |

Бит состояния, указывающий причину последнего сброса. Если имеется несколько сбросов, регистр содержит только последнее событие.

00: Сброс при включении питания и обнаружение отключения питания

01: внешний сброс

10: Сброс сторожевого таймера

11: сброс потери часов

|

| 2:1 | - | 00 | R | Зарезервированный |

| 0 | CLK32K | 0 | R | Тактовый сигнал 32 кГц (синхронизированный с системными часами) |

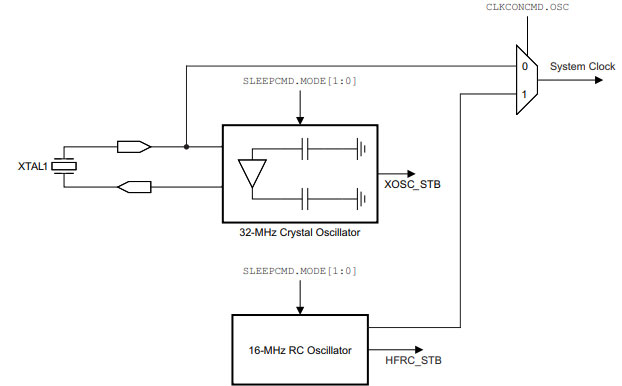

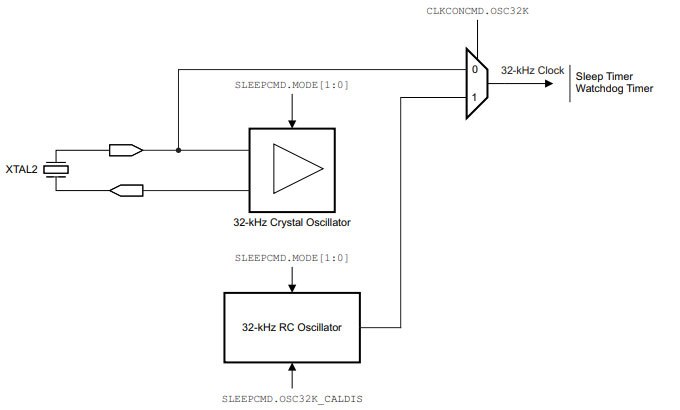

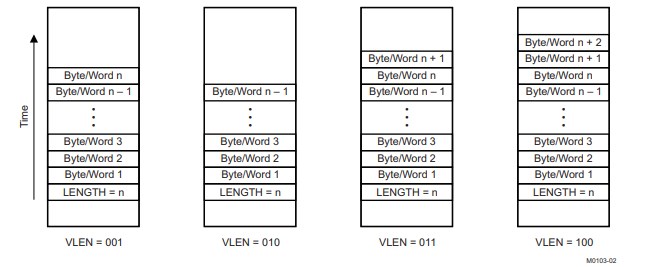

Рисунок 4-1. Обзор системы часов

4.4 Генераторы и часы

Существует также один источник тактовой частоты 32 кГц, который может быть либо генератором RC, либо кварцевым генератором, также управляемым регистром CLKCONCMD.

Регистр CLKCONSTA - это регистр только для чтения, используемый для получения текущего статуса часов.

Выбор генератора позволяет найти компромисс между высокой точностью в случае кварцевого генератора и низким энергопотреблением при использовании RC-генератора. Обратите внимание, что работа радиочастотного приемопередатчика требует использования кварцевого генератора 32 МГц.

В CC2533, CC2540 и CC2541 доступен дополнительный модуль для определения стабильности XOSC 32 МГц. Этот амплитудный детектор может быть полезен в средах со значительным шумом на источнике питания, чтобы гарантировать, что источник синхронизации не используется, пока тактовый сигнал не стабилизируется. В CC2533 этот модуль можно включить, установив бит SRCRC.XOSC_AMP_DET_EN, и это добавляет около 20 мкс ко времени запуска 32-МГц XOSC. В CC2540 и CC2541 модуль всегда включен.

4.4.1 Осцилляторы

Рисунок 4-1 дает обзор системы часов с доступными источниками часов.

- 32-МГц кварцевый генератор

- 16-МГц RC генератор

Время запуска кварцевого генератора на 32 МГц может быть слишком длинным для некоторых применений; следовательно, устройство может работать на 16-МГц RC генераторе до тех пор, пока кварцевый генератор не станет стабильным. 16-МГц RC генератор потребляет меньше энергии, чем кварцевый генератор, но поскольку он не так точен, как кварцевый генератор, его нельзя использовать для работы радиочастотного приемопередатчика.

- 32-кГц кварцевый генератор

- 32-кГц RC генератор.

XOSC 32 кГц разработан для работы на частоте 32,768 кГц и обеспечивает стабильный тактовый сигнал для систем, требующих точности по времени. RCOSC 32 кГц работает при калибровке 32,753 кГц. Калибровка может выполняться только при включенной 32-МГц XOSC, и эту калибровку можно отключить, включив бит SLEEPCMD.OSC32K_CALDIS. RCOSC 32 кГц следует использовать для снижения затрат и энергопотребления по сравнению с решением XOSC 32 кГц. Два генератора с частотой 32 кГц не могут работать одновременно.

4.4.2 Системные часы

Системные часы получены из выбранного источника системных часов, который является 32-МГц XOSC или 16-МГц RCOSC. Бит LKCONCMD.OSC выбирает источник системных часов. Обратите внимание, что для использования радиочастотного трансивера, кварцевый генератор 32 МГц должен быть выбран и устойчивым.

Обратите внимание, что изменение бита CLKCONCMD.OSC не приводит к мгновенному изменению системных часов. Изменение источника синхронизации вступает в силу, когда CLKCONSTA.OSC = CLKCONCMD.OSC. Это связано с требованием иметь стабильные часы до фактического изменения источника синхронизации. Также обратите внимание, что бит CLKCONCMD.CLKSPD отражает частоту системных часов и, следовательно, является зеркалом бита CLKCONCMD.OSC.

ПРИМЕЧАНИЕ. Переключение с источника тактовой частоты 16 МГц на источник тактовой частоты 32 МГц (и наоборот) согласуется с настройкой CLKCONCMD.TICKSPD. Медленная настройка CLKCONCMD.TICKSPD при изменении CLKCONCMD.OSC приводит к более длительному времени, прежде чем фактическое изменение источника вступит в силу. Самое быстрое переключение достигается, когда CLKCONCMD.TICKSPD равен 000.

ПРИМЕЧАНИЕ. После выхода из PM1, PM2 или PM3 ЦП должен дождаться, пока CLKCONSTA.OSC станет равным 0, прежде чем начнутся операции, требующие запуска системы на 32-МГц XOSC (например, радиосвязи).

4.4.3 32-кГц генераторы

Два генератора с частотой 32 кГц присутствуют в устройстве в качестве источников тактовых импульсов для тактовой частоты 32 кГц:

- 32 кГц XOSC

- 32-кГц RCOSC

По умолчанию после сброса RCOSC 32 кГц включается и выбирается в качестве источника тактовой частоты 32 кГц. RCOSC потребляет меньше энергии, но менее точен по сравнению с 32-кГц XOSC. Выбранный 32-кГц источник синхронизации управляет таймером сна, генерирует тик для сторожевого таймера и используется в качестве строба в таймере 2 для расчета времени сна таймера сна. Бит регистра CLKCONCMD.OSC32K выбирает генератор, который будет использоваться в качестве источника тактовой частоты 32 кГц. Этот бит не указывает на стабильность 32-кГц XOSC.

Бит регистра CLKCONCMD.OSC32K может быть записан в любое время, но он не вступает в силу, пока RCOSC 16 МГц не станет активным источником системных часов. Когда системная тактовая частота изменяется с 16-МГц RCOSC на 32-МГц XOSC (CLKCONCMD.OSC с 1 на 0), калибровка 32-кГц RCOSC запускается и выполняется один раз, если выбран 32-кГц RCOSC. Во время калибровки используется разделенная версия 32-МГц XOSC. Результатом калибровки является то, что RSOSC с частотой 32 кГц работает на частоте 32,753 кГц. Калибровка RCOSC 32 кГц может занять до 2 мсек. Калибровку можно отключить, установив для SLEEPCMD.OSC32K_CALDIS значение 1. В конце калибровки может возникнуть дополнительный импульс на тактовом источнике с частотой 32 кГц, что приведет к увеличению таймера отключения на 1.

4.4.4 Генератор и тактовые регистры

CLKCONCMD (0xC6) – Clock Control Command - команда управления часами

| Bit | Name | Reset | R/W | Description |

| 7 | OSC32K | 1 | R/W |

Выбор источника синхронизации 32 кГц. Установка этого бита инициирует только изменение источника синхронизации.

CLKCONSTA.OSC32K отражает текущую настройку. RCOSC на 16 МГц должен быть выбран в качестве системных часов, когда этот бит должен быть изменен. Этот бит не указывает на стабильность 32-кГц XOSC.

0: 32 кГц XOSC

1: 32 кГц RCOSC

|

| 6 | OSC | 1 | R/W |

Выбор источника системных часов. Установка этого бита инициирует только изменение источника синхронизации.

CLKCONSTA.OSC отражает текущую настройку.

0: 32 МГц XOSC

1: 16 МГц RCOSC

|

| 5:3 | TICKSPD[2:0] | 001 | R/W |

Таймер тиков настройки выхода. Не может быть выше настройки системных часов, заданной настройкой бита OSC.

000: 32 МГц

001: 16 МГц

010: 8 МГц

011: 4 МГц

100: 2 МГц

101: 1 МГц

110: 500 кГц

111: 250 кГц

Обратите внимание, что CLKCONCMD.TICKSPD можно установить на любое значение, но эффект ограничен настройкой CLKCONCMD.OSC; то есть, если CLKCONCMD.OSC = 1 и CLKCONCMD.TICKSPD = 000, CLKCONSTA.TICKSPD читает 001, а реальный TICKSPD составляет 16 МГц.

|

| 2:0 | CLKSPD | 001 | R/W |

Тактовая частота. Не может быть выше настройки системных часов, заданной настройкой бита OSC. Указывает текущую системную тактовую частоту

000: 32 МГц

001: 16 МГц

010: 8 МГц

011: 4 МГц

100: 2 МГц

101: 1 МГц

110: 500 кГц

111: 250 кГц

Обратите внимание, что CLKCONCMD.CLKSPD можно установить на любое значение, но эффект ограничен настройкой CLKCONCMD.OSC; то есть если CLKCONCMD.OSC = 1 и CLKCONCMD.CLKSPD = 000,

CLKCONSTA.CLKSPD читает 001, а реальный CLKSPD - 16 МГц.

Также обратите внимание, что отладчик нельзя использовать с разделенными системными часами. При запуске отладчика значение CLKCONCMD.CLKSPD должно быть установлено на 000, когда CLKCONCMD.OSC = 0, или на 001, когда CLKCONCMD.OSC = 1.

|

CLKCONSTA (0x9E) – Clock Control Status - Состояние управления часами

| Bit | Name | Reset | R/W | Description |

| 7 | OSC32K | 1 | R |

Текущий выбранный источник тактовой частоты 32 кГц:

0: 32 кГц XOSC

1: 32 кГц RCOSC

|

| 6 | OSC | 1 | R |

Текущие системные часы выбраны:

0: 32-МГц XOSC

1: 16 МГц RCOSC

|

| 5:3 | TICKSPD[2:0] | 001 | R |

Текущий таймер

000: 32 МГц

001: 16 МГц

010: 8 МГц

011: 4 МГц

100: 2 МГц

101: 1 МГц

110: 500 кГц

111: 250 кГц

|

| 2:0 | CLKSPD | 001 | R |

Текущая тактовая частота

000: 32 МГц

001: 16 МГц

010: 8 МГц

011: 4 МГц

100: 2 МГц

101: 1 МГц

110: 500 кГц

111: 250 кГц

|

4.5 Генерация тактов таймера

Значение регистра CLKCONCMD.TICKSPD управляет глобальным предварительным масштабированием для Таймера 1, Таймера 3 и Таймера 4. Значение предварительного масштабирования может быть установлено в диапазоне от 0,25 МГц до 32 МГц. Следует отметить, что если CLKCONCMD.TICKSPD указывает более высокую частоту, чем системные часы, фактическое значение предварительного масштабирования, указанное в CLKCONSTA.TICKSPD, совпадает с системными часами.

4.6 Хранение данных

В режимах питания PM2 и PM3 питание отключается от большей части внутренних цепей. Однако SRAM сохраняет свое содержимое, а содержимое внутренних регистров также сохраняется в PM2 и PM3.

Все регистры CPU, RF и периферийные устройства сохраняют свое содержимое в PM2 и PM3, кроме регистров AES, I2C и USB, OBSSEL0 – OBSSEL5, TR0 и в CC2541, LLECTRL.

Переключение в режимы с низким энергопотреблением PM2 или PM3 выглядит прозрачным для программного обеспечения. Обратите внимание, что значение таймера сна не сохраняется в PM3.

Все регистры сохраняют свои значения в PM1.

7 I/O Ports - Порты ввода/вывода

Порты ввода / вывода имеют следующие ключевые функции:

- 21 цифровой вход / выход

- Универсальный ввод / вывод или периферийный ввод / вывод

- Возможность подтягивания или опускания на входах

- Возможность внешнего прерывания

Тема ................................................. .................................................. ........................ страница

7.1 Неиспользуемые выводы ввода/вывода

7.2 Низкое напряжение питания ввода/вывода

7.3 Универсальный ввод/вывод

Все порты имеют как битовую, так и байтовую адресацию через регистры SFR P0, P1 и P2. Каждый вывод порта может быть индивидуально настроен для работы в качестве универсального ввода-вывода или периферийного ввода-вывода.

Регистры PxSEL, где x - это номер порта 0–2, используются для конфигурирования каждого контакта в порте в качестве вывода ввода-вывода общего назначения или в качестве периферийного сигнала ввода-вывода. По умолчанию после сброса все цифровые входные/выходные контакты настроены как входные контакты общего назначения.

Чтобы изменить направление вывода порта, регистры PxDIR используются для установки каждого вывода порта в качестве входа или выхода. Таким образом, установив соответствующий бит в PxDIR на 1, соответствующий вывод становится выходом.

При использовании в качестве входа выводы порта ввода/вывода общего назначения могут быть настроены на подтягивание, опускание или третье состояние. По умолчанию после сброса входы настраиваются как входы с подтягиванием. Отмените выбор функции pullup или pulldown на входе, соответствующий бит в PxINP должен быть установлен в 1.

В режимах питания PM1, PM2 и PM3 контакты ввода / вывода сохраняют режим ввода/вывода и выходное значение (если применимо), которое был установлен при вводе PM1, PM2 или PM3.

7.4 Прерывания ввода / вывода общего назначения

- IEN1.P0IE: разрешение прерывания P0

- IEN2.P1IE: разрешение прерывания P1

- IEN2.P2IE: разрешение прерывания P2

Когда условие прерывания возникает на одном из выводов ввода / вывода, флаг состояния прерывания в соответствующем регистре флага прерывания P0-P2, P0IFG, P1IFG или P2IFG, устанавливается в 1. Флаг состояния прерывания устанавливается независимо от того, установлен ли Пин имеет свой набор разрешения прерываний. Когда прерывание обслуживается, флаг состояния прерывания очищается путем записи 0 в этот флаг. Этот флаг должен быть очищен до очистки порта ЦП флаг прерывания (PxIF). Это показано на рис. 2-4: между входной линией и PxIFG есть обнаружение краев, но между PxIFG и PxINT не обнаружено ни краев, ни одного выстрела. Практическое влияние этого является то, что написано в разделе 2.5.1

- P0IEN: прерывание P0 разрешено

- P1IEN: разрешение прерывания P1

- P2IEN: прерывание P2 разрешено

- PICTL: конфигурация фронта P0, P1 и P2

- P0IFG: флаги прерываний P0

- P1IFG: флаги прерываний P1

- P2IFG: флаги прерываний P2

7.5 Универсальный ввод/вывод DMA

Триггер IOC_0 активируется при возникновении прерывания на выводах P0. Триггер IOC_1 активируется при возникновении прерывания на выводах P1.

7.6 Периферийный ввод/вывод

Для USART и таймерного ввода-вывода, установка соответствующих битов PxSEL в 1 необходима для того, чтобы выходные сигналы на цифровом выводе ввода-вывода контролировались периферийным устройством. Для периферийных входов с цифровых выводов ввода / вывода это необязательно.

Обратите внимание, что периферийные устройства имеют два альтернативных расположения для своих выводов ввода / вывода; см. таблицу 7-1. Приоритет может быть установлен между периферийными устройствами, если присутствуют противоречивые настройки, относящиеся к отображению ввода / вывода (используя биты P2SEL.PRIxP1 и P2DIR.PRIP0). Можно использовать все комбинации, не вызывающие конфликтов.

Также обратите внимание, что периферийные устройства, которые имеют входные контакты, получают вход от контакта независимо от настройки PxINP, и это может влиять на состояние периферийного устройства. Например, UART должен быть очищен перед использованием, если на контакте RX могла быть активность перед тем, как использовать его в качестве контакта UART.

Таблица 7-1. Отображение контактов периферийных входов / выходов

|

Periphery/

Function

|

P0 | P1 | P2 | ||||||||||||||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | 4 | 3 | 2 | 1 | 0 | |

| ADC | A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 | T | ||||||||||||

|

Operational

amplifier

|

O | - | + | ||||||||||||||||||

|

Analog

comparator

|

+ | - | |||||||||||||||||||

|

USART 0 SPI

Alt. 2 |

C | SS | MO | MI | |||||||||||||||||

| M0 | MI | C | SS | ||||||||||||||||||

|

USART 0 UART

Alt. 2 |

RT | CT | TX | RX | |||||||||||||||||

| TX | RX | RT | CT | ||||||||||||||||||

|

USART 1 SPI

Alt. 2

|

MI | M0 | C | SS | |||||||||||||||||

| MI | M0 | C | SS | ||||||||||||||||||

|

USART 1 UART

Alt. 2

|

RX | TX | RT | CT | |||||||||||||||||

| RX | TX | RT | CT | ||||||||||||||||||

|

TIMER 1

Alt. 2

|

4 | 3 | 2 | 1 | 0 | ||||||||||||||||

| 3 | 4 | 0 | 1 | 2 | |||||||||||||||||

|

TIMER 3

Alt. 2

|

1 | 0 | |||||||||||||||||||

| 1 | 0 | ||||||||||||||||||||

|

TIMER 4

Alt. 2

|

1 | 0 | |||||||||||||||||||

| 1 | 0 | ||||||||||||||||||||

| 32-kHz XOSC | Q1 | Q2 | |||||||||||||||||||

| DEBUG | DC | DD | |||||||||||||||||||

| OBSSEL | 5 | 4 | 3 | 2 | 1 | 0 | |||||||||||||||

7.6.1 Таймер 1

PERCFG.T1CFG выбирает, использовать ли альтернативу 1 или альтернативу 2.

- 0: канал 0 захватывает или сравнивает вывод

- 1: канал 1 захватывает или сравнивает вывод

- 2: канал 2 захватывает или сравнивает вывод

- 3: Канал 3 захватывает или сравнивает вывод

- 4: канал 4 захватывает или сравнивает вывод

P2SEL.PRI1P1 и P2SEL.PRI0P1 выбирают порядок приоритета при назначении нескольких периферийных устройств для порта 1. Каналы таймера 1 имеют приоритет, когда первый установлен на низком уровне, а второй - на высоком.

7.6.2 Таймер 3

PERCFG.T3CFG выбирает, использовать ли альтернативу 1 или альтернативу 2.

- 0: канал 0 захватывает или сравнивает вывод

- 1: канал 1 захватывает или сравнивает вывод

7.6.3 Таймер 4

PERCFG.T4CFG выбирает, использовать ли альтернативу 1 или альтернативу 2.

- 0: канал 0 захватывает или сравнивает вывод

- 1: канал 1 захватывает или сравнивает вывод

7.6.4 USART 0

Регистр SFR бит PERCFG.U0CFG выбирает, использовать ли альтернативное 1 или альтернативное 2 местоположения.

UART:

- RX: RXDATA

- TX: TXDATA

- RT: RTS

- CT: CTS

- MI: MISO

- МО: МОСИ

- C: SCK

- SS: SSN

P2SEL.PRI3P1 и P2SEL.PRI0P1 выбирают порядок приоритета при назначении нескольких периферийных устройств для порта 1. USART 0 имеет приоритет, когда оба установлены на 0. Обратите внимание, что если выбран режим UART и аппаратное управление потоком отключено, таймер 1 или таймер 3 имеет приоритет использовать порты P1.2 и P1.3.

7.6.5 USART 1

Бит регистра SFR PERCFG.U1CFG выбирает, использовать ли альтернативное 1 или альтернативное 2 местоположения.

В таблице 7-1 сигналы USART 1 показаны следующим образом:

- RX: RXDATA

- TX: TXDATA

- RT: RTS

- CT: CTS

- MI: MISO

- МО: МОСИ

- C: SCK

- SS: SSN

P2SEL.PRI3P1 и P2SEL.PRI2P1 выбирают порядок приоритета при назначении нескольких периферийных устройств для порта 1. USART 1 имеет приоритет, когда первый установлен на 1, а последний на 0. Обратите внимание, что если выбран режим UART и аппаратное управление потоком отключено, USART 0 или Таймер 3 имеет приоритет для использования портов P1.4 и P1.5.

7.6.6 АЦП

- A0: вход АЦП 0

- A1: вход АЦП 1

- A2: вход АЦП 2

- A3: вход АЦП 3

- A4: АЦП вход 4

- A5: вход АЦП 5

- A6: вход АЦП 6

- A7: вход АЦП 7

- T: АЦП внешний пусковой контакт

Настройки в регистре APCFG переопределяют настройки в P0SEL.

7.6.7 Операционный усилитель и аналоговый компаратор

Настройки в регистре APCFG переопределяют настройки в P0SEL.

7.7 Интерфейс отладки

7.8 32-кГц вход XOSC

7.9 Тестовые выходные сигналы радио

7.10 Сигнал выключения питания MUX (PMUX)

Регистр PMUX может использоваться для вывода тактовой частоты 32 кГц и / или статуса цифрового регулятора напряжения.

Кроме того, статус цифрового регулятора напряжения может быть выведен на один из контактов P1. Когда бит DREGSTA установлен, выводится статус цифрового регулятора напряжения. DREGSTAPIN выбирает контакт P1 (см. Описание регистра PMUX для деталей). Когда DREGSTA установлен, все остальные конфигурации для выбранного контакта перезаписываются. Выбранный вывод выводит 1, когда на встроенный в кристалл цифровой регулятор напряжения 1,8 В подается питание (микросхема имеет регулируемую мощность). Выбранный вывод выводит 0 при отключении встроенного цифрового стабилизатора напряжения 1,8 В, то есть в PM2 и PM3.

7.11 I/O Registers - Регистры ввода / вывода

- P0: Port 0

- P1: Port 1

- P2: Port 2

- PERCFG: Peripheral-control register - Регистр периферийного контроля

- APCFG: Analog peripheral I/O configuration - Конфигурация аналогового периферийного ввода / вывода

- P0SEL: Port 0 function-select register - регистр выбора функции порта 0

- P1SEL: Port 1 function-select register - регистр выбора функции порта 1

- P2SEL: Port 2 function-select register - регистр выбора функции порта 2

- P0DIR: Port 0 direction register - регистр направления порта 0

- P1DIR: Port 1 direction register - регистр направления порта 1

- P2DIR: Port 2 direction register - регистр направления порта 2

- P0INP: Port 0 input-mode register - регистр режима ввода порта 0

- P1INP: Port 1 input-mode register - регистр режима ввода порта 1

- P2INP: Port 2 input-mode register - регистр режима ввода порта 2

- P0IFG: Port 0 interrupt-status flag register - регистр флага состояния прерывания порта 0

- P1IFG: Port 1 interrupt-status flag register - регистр флага состояния прерывания порта 1

- P2IFG: Port 2 interrupt-status flag register - регистр флага состояния прерывания порта 2

- PICTL: Interrupt edge register - регистр фронт прерывания

- P0IEN: Port 0 interrupt-mask register - регистр маски прерывания порта 0

- P1IEN: Port 1 interrupt-mask register - регистр маски прерывания порта 1

- P2IEN: Port 2 interrupt-mask register - регистр маски прерывания порта 2

- PMUX: Power-down signal-mux register - регистр мультиплексирования сигнала при отключении питания

- OBSSEL0: Observation output control register 0 - регистр управления выходом наблюдения 0

- OBSSEL1: Observation output control register 1 - регистр управления выходом наблюдения 1

- OBSSEL2: Observation output control register 2 - регистр управления выходом наблюдения 2

- OBSSEL3: Observation output control register 3 - регистр управления выходом наблюдения 3

- OBSSEL4: Observation output control register 4 - регистр управления выходом наблюдения 4

- OBSSEL5: Observation output control register 5 - регистр управления выходом наблюдения 5

P0 (0x80) – Port 0

| Bit | Name | Reset | R/W | Description |

| 7:0 | P0[7:0] | 0xFF | R/W | Порт 0. Порт ввода-вывода общего назначения. Бит-адресуемый из SFR. Этот внутренний регистр ЦП доступен для чтения, но не для записи из XDATA (0x7080). |

P1 (0x90) – Port 1

| Bit | Name | Reset | R/W | Description |

| 7:0 | P1[7:0] | 0xFF | R/W | Порт 1. Порт ввода-вывода общего назначения. Бит-адресуемый из SFR. Этот внутренний регистр ЦП доступен для чтения, но не для записи из XDATA (0x7090). |

P2 (0xA0) – Port 2

| Bit | Name | Reset | R/W | Description |

| 7:5 | - | 000 | R0 | Зарезервированный |

| 4:0 | P2[4:0] | 1 1111 | R/W | Порт 2. Порт ввода-вывода общего назначения. Бит-адресуемый из SFR. Этот внутренний регистр ЦП доступен для чтения, но не для записи из XDATA (0x70A0). |

PERCFG (0xF1) – Peripheral Control - Регистр периферийного контроля

| Bit | Name | Reset | R/W | Description |

| 7 | - | 0 | R0 | Зарезервированный |

| 6 | T1CFG | 0 | R/W |

Timer 1 I/O location

0: Alternative 1 location

1: Alternative 2 location

|

| 5 | T3CFG | 0 | R/W |

Timer 3 I/O location

0: Alternative 1 location

1: Alternative 2 location

|

| 4 | T4CFG | 0 | R/W |

Timer 4 I/O location

0: Alternative 1 location

1: Alternative 2 location

|

| 3:2 | - | 00 | R/W | Зарезервированный |

| 1 | U1CFG | 0 | R/W |

USART 1 I/O location

0: Alternative 1 location

1: Alternative 2 location

|

| 0 | U0CFG | 0 | R/W |

USART 0 I/O location

0: Alternative 1 location

1: Alternative 2 location

|

APCFG (0xF2) – Analog Peripheral I/O Configuration - Конфигурация аналогового периферийного ввода / вывода

| Bit | Name | Reset | R/W | Description |

| 7:0 | APCFG[7:0] | 0x00 | R/W |

Конфигурация аналогового периферийного ввода / вывода. APCFG [7: 0] выбирает P0.7 – P0.0 в качестве аналогового ввода / вывода.

0: аналоговый ввод / вывод отключен

1: аналоговый ввод / вывод включен

|

P0SEL (0xF3) – Port 0 Function Select - регистр выбора функции порта 0

| Bit | Name | Reset | R/W | Description |

| 7:0 | SELP0_[7:0] | 0x00 | R/W |

P0.7 to P0.0 function select

0: General-purpose I/O

1: Peripheral function

|

P1SEL (0xF4) – Port 1 Function Select - регистр выбора функции порта 1

| Bit | Name | Reset | R/W | Description |

| 7:0 | SELP1_[7:0] | 0x00 | R/W |

P1.7 to P1.0 function select

0: General-purpose I/O

1: Peripheral function

|

P2SEL (0xF5) – Port 2 Function Select and Port 1 Peripheral Priority Control - Выбор функции порта 2 и периферийное управление приоритетом порта 1

| Bit | Name | Reset | R/W | Description |

| 7 | - | 0 | R0 | Зарезервированный |

| 6 | PRI3P1 | 0 | R/W |

Порт 1 периферийный приоритет управления. Этот бит определяет, какой модуль имеет приоритет в случае, когда модули назначены на те же контакты.

0: USART 0 имеет приоритет.

1: USART 1 имеет приоритет

|

| 5 | PRI2P1 | 0 | R/W |

Порт 1 периферийный приоритет управления. Этот бит определяет порядок приоритета в случае, когда PERCFG назначает USART 1 и Timer 3 на одни и те же контакты.

0: USART 1 имеет приоритет.

1: Timer 3 имеет приоритет.

|

| 4 | PRI1P1 | 0 | R/W |

Порт 1 периферийный приоритет управления. Этот бит определяет порядок приоритета в случае, когда PERCFG назначает Timer 1 и Timer 4 одинаковым контактам.

0: Timer 1 имеет приоритет.

1: Timer 4 имеет приоритет.

|

| 3 | PRI0P1 | 0 | R/W |

Порт 1 периферийный приоритет управления. Этот бит определяет порядок приоритета в случае, когда PERCFG назначает USART 0 и Timer 1 для одних и тех же контактов.

0: USART 0 имеет приоритет.

1: Таймер 1 имеет приоритет.

|

| 2 | SELP2_4 | 0 | R/W |

P2.4 function select

0: General-purpose I/O

1: Peripheral function

|

| 1 | SELP2_3 | 0 | R/W |

P2.3 function select

0: General-purpose I/O

1: Peripheral function

|

| 0 | SELP2_0 | 0 | R/W |

P2.0 function select

0: General-purpose I/O

1: Peripheral function

|

P0DIR (0xFD) – Port 0 Direction - направление

| Bit | Name | Reset | R/W | Description |

| 7:0 | DIRP0_[7:0] | 0x00 | R/W |

P0.7 to P0.0 I/O direction

0: Input

1: Output

|

P1DIR (0xFE) – Port 1 Direction - направление

| Bit | Name | Reset | R/W | Description |

| 7:0 | DIRP1_[7:0] | 0x00 | R/W |

P1.7 to P1.0 I/O direction

0: Input

1: Output

|

P2DIR (0xFF) – Port 2 Direction and Port 0 Peripheral Priority Control - управление направлением порта 2 и периферийным приоритетом порта 0

| Bit | Name | Reset | R/W | Description |

| 7:6 | PRIP0[1:0] | 00 | R/W |

Порт 0 периферийный приоритет управления. Эти биты определяют порядок приоритета в случае когда PERCFG назначает несколько периферийных устройств одним и тем же контактам.

Подробный список приоритетов:

00:

1-й приоритет: USART 0

2-й приоритет: USART 1

3-й приоритет: Timer 1

01:

1-й приоритет: USART 1

2-й приоритет: USART 0

3-й приоритет: Timer 1

10:

1-й приоритет: Timer 1, channels 0–1

2-й приоритет: USART 1

3-й приоритет: USART 0

4-й приоритет: Timer1, channels 2–3

11:

1-й приоритет: Timer 1, channels 2–3

2-й приоритет: USART 0

3-й приоритет: USART 1

4-й приоритет: Timer 1, channels 0–1

|

| 5 | - | 0 | R0 | Зарезервированный |

| 4:0 | DIRP2_[4:0] | 0 0000 | R/W |

P2.4 to P2.0 I/O direction

0: Input

1: Output

|

P0INP (0x8F) – Port 0 Input Mode - режим ввода

| Bit | Name | Reset | R/W | Description |

| 7:0 | MDP0_[7:0] | 0x00 | R/W |

P0.7 to P0.0 I/O input mode

0: Pullup or pulldown [see P2INP (0xF7) – Port 2 input mode]

1: 3-state

|

P1INP (0xF6) – Port 1 Input Mode - режим ввода

| Bit | Name | Reset | R/W | Description |

| 7:0 | MDP1_[7:2] | 0000 00 | R/W |

P1.7 to P1.2 I/O input mode

0: Pullup or pulldown [see P2INP (0xF7) – Port 2 input mode]

1: 3-state

|

| 1:0 | - | 00 | R0 | Зарезервированный |

P2INP (0xF7) – Port 2 Input Mode - режим ввода

| Bit | Name | Reset | R/W | Description |

| 7 | PDUP2 | 0 | R/W |

Port 2 pull-or-pulldown выберите. Выбирает функцию для всех выводов порта 2, сконфигурированных как входы pull-or-pulldown.

0: Pullup

1: Pulldown

|

| 6 | PDUP1 | 0 | R/W |

Port 1 pull-or-pulldown выберите. Выбирает функцию для всех выводов порта 1, сконфигурированных как входы pull-or-pulldown.

0: Pullup

1: Pulldown

|

| 5 | PDUP0 | 0 | R/W |

Port 0 pull-or-pulldown выберите. Выбирает функцию для всех выводов порта 0, сконфигурированных как входы pull-or-pulldown.

0: Pullup

1: Pulldown

|

| 4:0 | MDP2_[4:0] | 0 0000 | R/W |

P2.4 to P2.0 I/O input mode

0: Pullup or pulldown

1: 3-state

|

P0IFG (0x89) – Port 0 Interrupt Status Flag - флаг состояния прерывания по порту 0

| Bit | Name | Reset | R/W | Description |

| 7:0 | P0IF[7:0] | 0x00 | R/W0 |

Порт 0, входы с 7 по 0, флаги состояния прерывания. Когда вывод входного порта имеет ожидающий запрос прерывания, устанавливается соответствующий флаг бита.

|

P1IFG (0x8A) – Port 1 Interrupt Status Flag - флаг состояния прерывания по порту 1

| Bit | Name | Reset | R/W | Description |

| 7:0 | P1IF[7:0] | 0x00 | R/W0 |

Порт 1, входы с 7 по 0, флаги состояния прерывания. Когда вывод входного порта имеет ожидающий запрос прерывания, устанавливается соответствующий флаг бита.

|

P2IFG (0x8B) – Port 2 Interrupt Status Flag - флаг состояния прерывания по порту 2

| Bit | Name | Reset | R/W | Description |

| 7:6 | - | 00 | R0 | Зарезервированный |

| 5 | DPIF | 0 | R/W0 | USB D+ interrupt-status flag.Этот флаг устанавливается, когда на линии D + имеется ожидающий запрос прерывания, и используется для обнаружения событий возобновления USB в состоянии приостановки USB. Этот флаг не устанавливается, когда USB-контроллер не приостановлен. |

| 4:0 | P2IF[4:0] | 0 0000 | R/W0 | Порт 2, входы с 4 по 0, флаги состояния прерывания. Когда вывод входного порта имеет ожидающий запрос прерывания, устанавливается соответствующий бит флага. |

PICTL (0x8C) – Port Interrupt Control - управление прерываниями порта

| Bit | Name | Reset | R/W | Description |

| 7 | PADSC | 0 | R/W |

Управление силой привода для выводов ввода / вывода в режиме вывода. Выбирает повышение мощности выходного привода для учета низкого напряжения питания ввода-вывода на выводе DVDD (это обеспечивает такую же прочность привода при более низких напряжениях и при более высоких).

0: увеличение минимальной силы привода. DVDD1 и DVDD2, равные или превышающие 2,6 В

1: максимальное усиление привода. DVDD1 и DVDD2 менее 2,6 В

|

| 6:4 | - | 000 | R0 | Зарезервированный |

| 3 | P2ICON | 0 | R/W |

Порт 2, входы от 4 до 0, конфигурация прерываний. Этот бит выбирает условие запроса прерывания для порта 2 входы с 4 по 0.

0: Rising edge Передний фронт на входе дает прерывание.

1: Falling edge Падающий фронт на входе дает прерывание.

|

| 2 | P1ICONH | 0 | R/W |

Порт 1, входы от 7 до 4, конфигурация прерываний. Этот бит выбирает условие запроса прерывания для порта 1 входы с 7 по 4.

0: Rising edge Передний фронт на входе дает прерывание.

1: Falling edge Падающий фронт на входе дает прерывание.

|

| 1 | P1ICONL | 0 | R/W |

Порт 1, входы от 3 до 0, конфигурация прерываний. Этот бит выбирает условие запроса прерывания для порта 1 входы с 3 по 0.

0: Rising edge Передний фронт на входе дает прерывание.

1: Falling edge Падающий фронт на входе дает прерывание.

|

| 0 | P0ICON | 0 | R/W |

Порт 0, входы от 7 до 0, конфигурация прерываний. Этот бит выбирает условие запроса прерывания для порта 0 входы с 7 по 0.

0: Rising edge Передний фронт на входе дает прерывание.

1: Falling edge Падающий фронт на входе дает прерывание.

|

P0IEN (0xAB) – Port 0 Interrupt Mask - маска прерывания порта 0

| Bit | Name | Reset | R/W | Description |

| 7:0 | P0_[7:0]IEN | 0x00 | R/W0 |

Разрешение прерывания от порта P0.7 до P0.0

0: прерывания отключены.

1: прерывания включены.

|

P1IEN (0x8D) – Port 1 Interrupt Mask - маска прерывания порта 1

| Bit | Name | Reset | R/W | Description |

| 7:0 | P1_[7:0]IEN | 0x00 | R/W0 |

Разрешение прерывания от порта P1.7 до P1.0

0: прерывания отключены.

1: прерывания включены.

|

P2IEN (0xAC) – Port 2 Interrupt Mask - маска прерывания порта 2

| Bit | Name | Reset | R/W | Description |

| 7:6 | - | 00 | R0 | Зарезервированный |

| 5 | DPIEN | 0 | R/W |

USB D+ разрешение прерывания

0: USB D+ прерывание отключено

1: USB D+ прерывание включено

|

| 4:0 | P2_[4:0]IEN | 0 0000 | R/W |

Разрешение прерывания от порта P2.4 до P2.0

0: прерывания отключены.

1: прерывания включены.

|

PMUX (0xAE) – Power-Down Signal Mux - мультиплексор при отключении питания

| Bit | Name | Reset | R/W | Description |

| 7 | CKOEN | 0 | R/W | Включение синхронизации. Когда этот бит установлен, выбранная тактовая частота 32 кГц выводится на один из выводов P0. CKOPIN выбирает пин-код для использования. Это переопределяет все другие конфигурации для выбранного контакта. Часы выводятся во всех режимах питания; однако в PM3 часы останавливаются (см. PM3 в главе 4). |

| 6:4 | CKOPIN[2:0] | 000 | R/W | Вывод синхронизации. Выбирает, какой вывод P0 будет использоваться для вывода выбранных тактовых импульсов 32 кГц. |

| 3 | DREGSTA | 0 | R/W | Состояние цифрового регулятора напряжения. Когда этот бит установлен, состояние цифрового регулятора напряжения выводится на один из выводов P1. DREGSTAPIN выбирает пин-код. Когда DREGSTA установлен, все остальные конфигурации для выбранного контакта перезаписываются. Выбранный вывод выводит 1, когда на встроенный в кристалл цифровой регулятор напряжения 1,8 В подается питание (микросхема имеет регулируемую мощность). Выбранный вывод выводит 0 при отключении встроенного цифрового стабилизатора напряжения 1,8 В. |

| 2:0 | DREGSTAPIN[2:0] | 000 | R/W | Digital Voltage Regulator Status Pin. Выбирает, какой вывод P1 будет использоваться для вывода сигнала DREGSTA. |

Обратите внимание, что регистры с OBSSEL0 по OBSSEL5 не сохраняют данные в состояниях PM2 и PM3.

OBSSEL0 (0x6243) – Observation Output Control Register 0 - регистр управления выходом наблюдений 0

| Bit | Name | Reset | R/W | Description |

| 7 | EN | 0 | R/W |

Бит управления выводом наблюдения 0 на P1 [0].

0 - Выход наблюдения отключен

1 - Выход наблюдения включен

Примечание. Если этот параметр включен, он переписывает стандартное поведение GPIO P1.0.

|

| 6:0 | SEL[6:0] | 000 0000 | R/W |

Выберите выходной сигнал на выходе наблюдения 0

111 1011 (123): rfc_obs_sig0

111 1100 (124): rfc_obs_sig1

111 1101 (125): rfc_obs_sig2

Другие: Зарезервированны

|

OBSSEL1 (0x6244) – Observation Output Control Register 1 - регистр управления выходом наблюдений 1

| Bit | Name | Reset | R/W | Description |

| 7 | EN | 0 | R/W |

Бит управления выводом наблюдения 1 на P1 [1].

0 - Выход наблюдения отключен

1 - Выход наблюдения включен

Примечание. Если этот параметр включен, он переписывает стандартное поведение GPIO P1.1.

|

| 6:0 | SEL[6:0] | 000 0000 | R/W |

Выберите выходной сигнал на выходе наблюдения 1

111 1011 (123): rfc_obs_sig0

111 1100 (124): rfc_obs_sig1

111 1101 (125): rfc_obs_sig2

Другие: Зарезервированны

|

OBSSEL2 (0x6245) – Observation Output Control Register 2 - регистр управления выходом наблюдений 2

| Bit | Name | Reset | R/W | Description |

| 7 | EN | 0 | R/W |

Бит управления выводом наблюдения 2 на P1 [2].

0 - Выход наблюдения отключен

1 - Выход наблюдения включен

Примечание. Если этот параметр включен, он переписывает стандартное поведение GPIO P1.2.

|

| 6:0 | SEL[6:0] | 000 0000 | R/W |

Выберите выходной сигнал на выходе наблюдения 2

111 1011 (123): rfc_obs_sig0

111 1100 (124): rfc_obs_sig1

111 1101 (125): rfc_obs_sig2

Другие: Зарезервированны

|

OBSSEL3 (0x6246) – Observation Output Control Register 3 - регистр управления выходом наблюдений 3

| Bit | Name | Reset | R/W | Description |

| 7 | EN | 0 | R/W |

Бит управления выводом наблюдения 3 на P1 [3].

0 - Выход наблюдения отключен

1 - Выход наблюдения включен

Примечание. Если этот параметр включен, он переписывает стандартное поведение GPIO P1.3.

|

| 6:0 | SEL[6:0] | 000 0000 | R/W |

Выберите выходной сигнал на выходе наблюдения 3

111 1011 (123): rfc_obs_sig0

111 1100 (124): rfc_obs_sig1

111 1101 (125): rfc_obs_sig2

Другие: Зарезервированны

|

OBSSEL4 (0x6247) – Observation Output Control Register 4 - регистр управления выходом наблюдений 4

| Bit | Name | Reset | R/W | Description |

| 7 | EN | 0 | R/W |

Бит управления выводом наблюдения 4 на P1 [4].

0 - Выход наблюдения отключен

1 - Выход наблюдения включен

Примечание. Если этот параметр включен, он переписывает стандартное поведение GPIO P1.4.

|

| 6:0 | SEL[6:0] | 000 0000 | R/W |

Выберите выходной сигнал на выходе наблюдения 4

111 1011 (123): rfc_obs_sig0

111 1100 (124): rfc_obs_sig1

111 1101 (125): rfc_obs_sig2

Другие: Зарезервированны

|

OBSSEL5 (0x6248) – Observation Output Control Register 5 - регистр управления выходом наблюдений 5

| Bit | Name | Reset | R/W | Description |

| 7 | EN | 0 | R/W |

Бит управления выводом наблюдения 5 на P1 [5].

0 - Выход наблюдения отключен

1 - Выход наблюдения включен

Примечание. Если этот параметр включен, он переписывает стандартное поведение GPIO P1.5.

|

| 6:0 | SEL[6:0] | 000 0000 | R/W |

Выберите выходной сигнал на выходе наблюдения 5

111 1011 (123): rfc_obs_sig0

111 1100 (124): rfc_obs_sig1

111 1101 (125): rfc_obs_sig2

Другие: Зарезервированны

|

8 DMA Controller - DMA контроллер

Контроллер DMA координирует все передачи DMA, гарантируя, что запросы DMA имеют соответствующий приоритет по отношению друг к другу и к доступу к памяти ЦП. Контроллер прямого доступа к памяти содержит ряд программируемых каналов прямого доступа к памяти для перемещения данных память-память.

Основные характеристики контроллера прямого доступа к памяти следующие:

- Пять независимых каналов DMA

- Три настраиваемых уровня приоритета канала DMA

- 32 настраиваемых триггерных события передачи

- Независимый контроль исходного и конечного адресов

- Одиночный, блочный и повторный режимы передачи

- Поддерживает поле длины в передаваемых данных, устанавливая переменную длину передачи

- Может работать в режиме размера слова или размера байта.

8.1 DMA Operation - Работа с прямым доступом к памяти

Чтобы использовать канал DMA, его необходимо сначала настроить, как описано в Разделе 8.2 и Разделе 8.3.

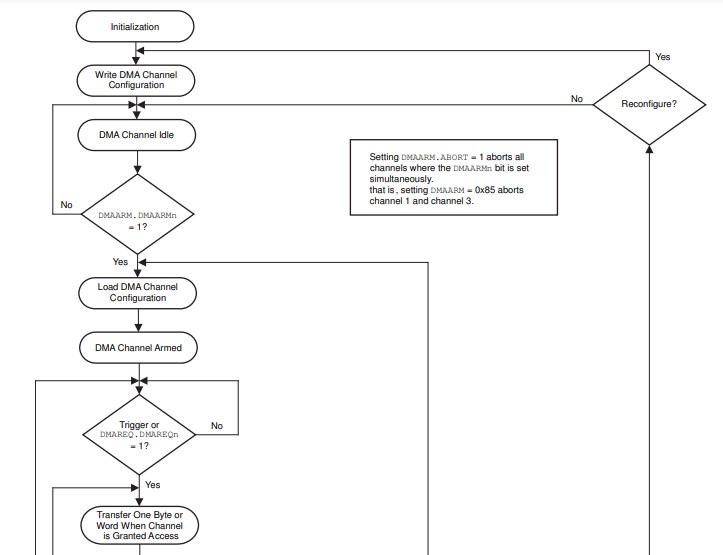

На рис. 8-1 показана диаграмма состояний DMA. После того, как канал DMA настроен, он должен быть активирован, прежде чем будет разрешена любая передача. Канал DMA активируется установкой соответствующего бита в регистре DMAARM канала DMA.

В дополнение к запуску передачи DMA через триггерные события DMA пользовательское программное обеспечение может принудительно начать передачу DMA, установив соответствующий бит DMAREQ.

Бит DMAREQ очищается только тогда, когда происходит соответствующая передача DMA. Бит DMAREQ не сбрасывается, когда канал снят с охраны.

Рисунок 8-1. Операция прямого доступа к памяти

8.2 DMA Configuration Parameters - Параметры конфигурации прямого доступа к памяти

Поведение каждого из пяти каналов прямого доступа к памяти настраивается со следующими параметрами:

Подробное описание всех параметров конфигурации дано в разделах с 8.2.1 по 8.2.11.

8.2.1 Адрес источника

8.2.2 Адрес назначения

8.2.3 Счетчик передач

Количество байтов/слов, которые должны быть переданы для завершения передачи DMA. Когда количество передач достигнуто, контроллер DMA перезаряжает или снимает с охраны канал DMA и предупреждает ЦП с запросом на прерывание. Счетчик передач может быть определен в конфигурации или может быть определен как переменная длина, как описано в Разделе 8.2.4.

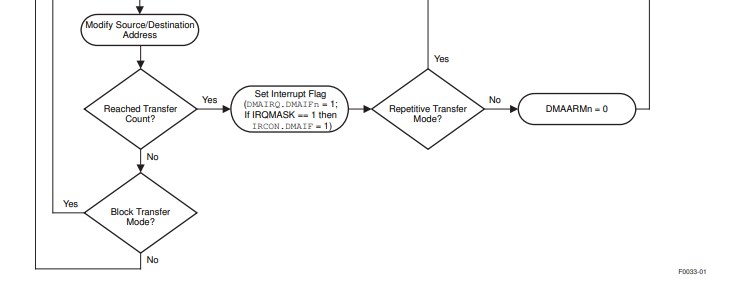

8.2.4 Настройка VLEN

Обратите внимание, что бит M8 (раздел 8.2.11) используется только тогда, когда выбрана передача размером в байт.

- Передача количества байтов или слов, заданных первым байтом/словом + 1 (передается длина байта/слова, а затем столько байтов/слов, сколько диктуется длиной байта/слова)

- Передача количества байтов или слов, которыми управляет первый байт/слово

- Передача количества байтов или слов, заданных первым байтом/словом + 2 (передается длина байта/слова, а затем столько байтов/слов, сколько указано длиной байта/слова + 1)

- Передача количества байтов или слов, заданных первым байтом/словом + 3 (передается длина байта/слова, а затем столько байтов/слов, сколько указано длиной байта/слова + 2)

Рисунок 8-2 показывает опции VLEN.

Рисунок 8-2. Варианты передачи переменной длины (VLEN)

8.2.5 Триггерное событие

8.2.6 Приращение источника и назначения

- Увеличение на ноль. Указатель адреса остается фиксированным после каждой передачи.

- Увеличение на единицу. Указатель адреса увеличивается на один счетчик после каждой передачи.

- Увеличение на два. Указатель адреса увеличивается на два счетчика после каждой передачи.

- Уменьшить на единицу. Указатель адреса уменьшается на один счетчик после каждой передачи.

8.2.7 Режим передачи DMA

8.2.8 Приоритет прямого доступа к памяти

Схема используется для обеспечения доступа для всех. Существует три уровня приоритета прямого доступа к памяти:

8.2.9 Передача байтов или слов

8.2.10 Маска прерывания

8.2.11 Настройка режима 8

Это поле определяет, использовать ли 7 или 8 бит на байт для длины передачи. Применимо только при передаче байтов.

8.3 Настройка конфигурации прямого доступа к памяти

Важно отметить, что метод указания начального адреса для структуры данных конфигурации DMA отличается для канала DMA 0 и каналов DMA 1–4 следующим образом:

Таким образом, DMA-контроллер ожидает, что структуры данных конфигурации DMA для каналов DMA 1–4 будут лежать в непрерывной области памяти, начиная с адреса, хранящегося в DMA1CFGH:DMA1CFGL, и состоящего из 32 байт.

8.4 Остановка передачи DMA

8.5 Прерывания прямого доступа к памяти

8.6 Структура данных конфигурации DMA

8.7 DMA Memory Access - Доступ к памяти прямого доступа к памяти

Таблица 8-1. Источники триггеров прямого доступа к памяти

| DMA Trigger | Functional Unit | Description | |

| Number | Name | ||

| 0 | NONE | DMA | Нет триггера, установка бита DMAREQ.DMAREQx запускает передачу. |

| 1 | PREV | DMA | Канал DMA запускается завершением предыдущего канала. |

| 2 | T1_CH0 | Timer 1 | Таймер 1, сравнение, канал 0 |

| 3 | T1_CH1 | Timer 1 | Таймер 1, сравнение, канал 1 |

| 4 | T1_CH2 | Timer 1 | Таймер 1, сравнение, канал 2 |

| 5 | T2_EVENT1 | Timer 2 | Таймер 2, импульс события 1 |

| 6 | T2_EVENT2 | Timer 2 | Таймер 2, импульс события 2 |

| 7 | T3_CH0 | Timer 3 | Таймер 3, сравнение, канал 0 |

| 8 | T3_CH1 | Timer 3 | Таймер 3, сравнение, канал 1 |

| 9 | T4_CH0 | Timer 4 | Таймер 4, сравнение, канал 0 |

| 10 | T4_CH1 | Timer 4 | Таймер 4, сравнение, канал 1 |

| 11 | ST | Sleep Timer (not in CC2540/41) | Таймер сна сравнить |

| RADIO1 | Radio (CC2541) | Радиотриггер DMA 1 (см. Раздел 25.3.2) | |

| 12 | IOC_0 | I/O controller | Переход порта 0 (1) |

| 13 | IOC_1 | I/O controller | Переход порта 1 (1) |

| 14 | URX0 | USART 0 | USART 0 RX завершен |

| 15 | UTX0 | USART 0 | USART 0 TX завершен |

| 16 | URX1 | USART 1 | USART 1 RX завершен |

| 17 | UTX1 | USART 1 | USART 1 TX завершен |

| 18 | FLASH | Flash controller | Запись данных на флеш завершена |

| 19 | RADIO | Radio (not in CC2540) |

CC253x: Получен байт RF-пакета (см. Раздел 23.3)

CC2541: триггер Radio DMA 0 (см. раздел 25.3.2)

|

| 20 | ADC_CHALL | ADC | Конец преобразования АЦП в последовательности, образец готов |

| 21 | ADC_CH11 | ADC | Конец АЦП канала преобразования 0 в последовательности, образец готов |

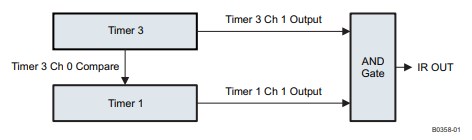

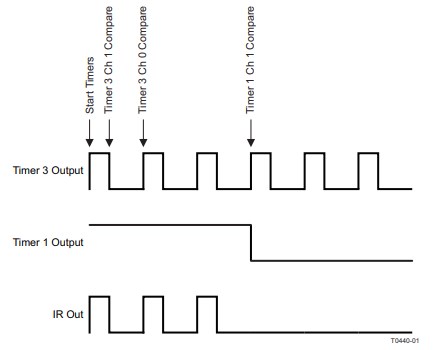

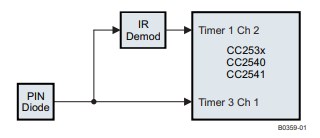

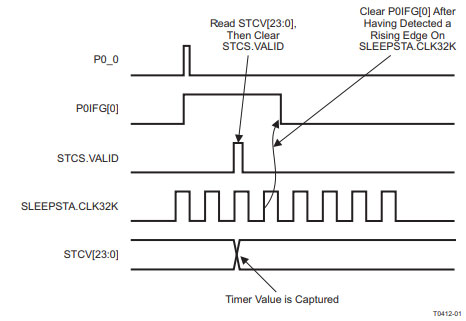

| 22 | ADC_CH21 | ADC | Конец АЦП канала преобразования 1 в последовательности, образец готов |